| |

|

|

Главная » Книги и журналы 1 ... 31 32 33 34 35 36 37 38 12.5. ПРИМЕРЫ CHCTEft-i ЦИФРОВОЙ ОБРАБОТКИ АНАЛОГОВЫХ СИГНАЛОВ Быстрое совершенствование параметров цифровых микросхем и БИС, создание микропроцессоров и сигнальных процессоров, работающих в реальном масштабе времени, сделали сейчас экономически и технически целесообразной цифровую обработку аналоговых сигналов. К основным преимуществам цифровой обработки по сравнению с традиционной аналоговой можно отнести [2]: выполнение одним прибором различных функций за счет изменения программы работы; обработка различных сигналов за счет введения мультиплексирования; выполнение алгоритмов обработки любой сложности без потерь точности; высокая помехоустойчивость и воспроизводимость результатов. Среди недостатков цифровой обработки основными пока являются сравнительно невысокая частота обрабатываемых аналоговых сигналов (около 1 МГц) и зависимость этой частоты от требуемой точности. Существенными- также являются ошибки округления и нелинейные эффекты переполнения, обусловленные особенностью традиционной гарвардской архитектуры сигнального процессора. Частично устранить эти недостатки можно за счет усложнения алгоритмов и, как следствие, дополнительных аппаратурных затрат. В таких системах АЦП обеспечивают тактируемую выборку мгновенных значений аналоговых сигналов и затем в ОЗУ длительное хранение результатов преобразования без потери информации. Затем цифровые приборы, выполненные на жесткой логике или на программируемых сигнальных процессорах, позволяют в реальном масштабе времени произвести обработку аналоговых величин. Таким образом, в современной аппаратуре реализуются растяжение и сжатие аналоговых сигналов во времени, запись и хранение изменений аналоговых величин за конечные промежутки времени, цифровая фильтрация сигналов, быстрое преобразование Фурье, синтез музыкальных фрагментов и речевых сигналов, кодирование и цифрование информации для повышения помехоустойчивости и засекречивания и т. д. При этом кроме упомянутых выше ошибок округления к погрешности обработки добавляются только ошибки дискретизации по амплитуде и времени. Для реализации алгоритмов цифровой обработки сигналов могут использоваться и современные .16-разрядные универсальные микроЭВМ, если частотный диапазон аналоговых сигналов ограничен 100 Гц. Объясняется это тем, что при реализации практически всех алгоритмов цифровой обработки основными операциями являются умножение и сложение. Выполнение же последовательности этих операций при использовании, например, современной микроЭВМ на базе 1806ВМ2 с традиционной архитектурой фон Неймана потребует времени более 100 мкс. Поскольку за период дискретиза-

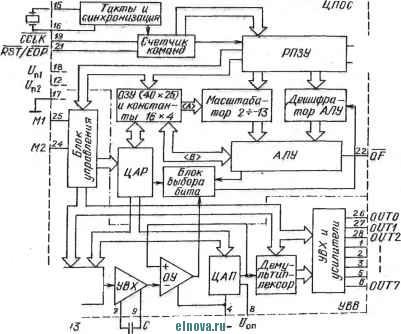

свбиго,  РйС: \Ш. Сгруктурмйй схема аналого-цмфревой линии задержки ции ДОЛЖНО обычно выпблнйться Несколько десятков носледователь-ностей таких онераций, то становится номятной низкйй эффективность применений микроирбцессорных наборов для решений задач цифровой обработки аналоговых сигналов в реальном масштабе времени. Исходя из сказанного ясно, почему до сих пор ведутсй активные разработки систем цифровой обработки аналоговых сигналов на базе анйлогоёых и цифровых ВИС общего применения, некоторые из которых приведены ниже. На рис. 12.8 Приведена структурная схема анаЛОГо-цифроВой линии задержки. Частота дискретизации аналогового сигнала согласно теореме выборки должна быть по крайней мере вдйое больше наивысшей частотной составляющей аналогового сигнала. Время выборки УВХ и время преобразования АЦП совместно определяют максимальное значение частоты дискретизации. Как только п-разрядные цифровые выборки появляются в виде слов в параллельном коде на выходе АЦП, они тактовым импульсом записываются в регистр сдвига, а ранее полученные выборки сдвигаются по регистру слева Направо. В процессе такой работы К цифровых выборок заполняют Л^-разрядныЙ регистр, а значения выборок, которые появляются на выходе регистра сдвига, восстанавливаются в аналоговую форму с помощью ЦАП. Восстановленный аналоговый сигнал представляет собой задержанную во времени копию исходного аналогового входного сигнала. Время задержки h зависит от частоты дискретизации /д и числа разрядов К в регистрах сдвига: h = K/f, Параллельный регистр сдвига можно заменить последовательным, в который значения разрядов цифровой выборки загружаются поочередно В этом случае на выходе АЦП требуется преобразователь параллельного кода в последовательный, а на йходе ЦАП необходимо выполнить обратное преобразование. Переход к последовательному регистру й N раз уменьшит быстродействие такой линии задержки, поэтому последовательная система удобна для аналоговых сигналой, не требующих высокой частоты дискретизации. Приведенная линия задержки находит широкое применение В студиях звукозаписи для воспроизведения различных звуковых эффектов, получаемых при одновременном воспроизведении двух идентичных сигналов, но сдвинутых между собой во времени. До изобретения электронных линий задержки такие эффекты получали t помощью двух лентопротяжных механизмов, один из которых имел изменяемую скорость. Структура показанной линии задержки может быть использована для создания эффектов эха или реверберации, й также для умножения звука музыкального йНструмейта. Например, скрипка, звучащая совместно с задержанной во времени, скажем, на 5 мс копией, зйучит как две скрипки. Если повторно пропустить сигнал через линию задержки, то получится звук, подобный звучанию четырех скрипок. Можно создать эффект йвучаНйЯ целой группы струнных инструментов из одной скриПкй с ПОМОЩЬ такой линии задержки и МногОдОрожечного записьШающего устройства. Используя возможность рециркуляции в памяти Нй регистре сдвига, можно построить устройство, регистрирующее переходной процесс аналогового события, и таким образом реализовать осциллограф с запоминанием. Система регистрации и хранения переходных процессов полезна для изучения аналоговых переменных во многих областях исследований, например при анализе биологических сигналов и ударных колебаний, при механических разрушающих испытаниях компонентов. Функциональная схема, иллюстрирующая использование АЦП и Памяти на регистре сдвига в качестве записывающего устройства переходных процессов, аналогична приведенной на рис. 12.8. Схема управления и синхронизации инициирует последовательность выборок, синхронизированных с началом переходного сигнала, который необходимо записать. Последовательность выборок прекращаеТсй при заполнении регистра сдвига. Частота дискретизации выбирается таким образом, чтобы выборки можно было производить в течение всего времени переходного процесса, который необходимо записать. Запомненная информация постоянно перемещается в регистрах и через определенные промежутки времени восстанавливается в аналоговую форму с. помощью ЦАП, чтобы получить ее изображение на экране осциллографа. Информация может сдвигаться с тактовой частотой, отличающейся от той, с которой она вводится в память. Это позволяет преобразование и отображение аналогового переходного процесса осуществлять с произвольной скоростью. Например, данные об изменениях параметров быстрого переходного процесса можно вывести из блока памяти со скоростью, совместимой со скоростью перемещения пера самописца. Наоборот, если реальный переходной процесс происходит медленно, то данные об изменении его параметров можно выводить с большей тактовой частотой, чтобы получить без мерцания изображение на экране осциллографа. При этом регистр сдвига памяти должен работать в режиме рециркуляции. Если требуется постоянная циф ровая запись переходных процессов, то содержимое регистров сдвига просто переписывается в какую-нибудь цифровую память длительного хранения. Описанная схема может быть использована для построения генераторов повторяющихся аналоговых сигналов произвольной формы. В регистр сдвига загружается информация о требуемом колебании, которую можно заложить в аналоговой форме с помощью АЦП или, если требуется, в цифровом виде прямо в регистр. Загрузку можно осуществить медленно (вручную, одну выборку за один раз, если это необходимо). Когда регистр переходит в режим рециркуляции, информация может сдвигаться по кругу постоянно. Она принимает вид периодического аналогового колебания с помощью выходного ЦАП. Частота повторения управляется тактовой частотой регистра сдвига. Оперативные запоминающие устройства обеспечивают еще большую универсальность по отношению к памяти с последовательной выборкой на регистрах сдвига. Обычно емкость памяти ОЗУ характеризуют числом слов, которые могут запоминаться в памяти, и числом разрядов в каждом слове. В режиме записи ОЗУ позволяет ввести в определенное место памяти информацию, присутствующую на входных шинах, а в режиме считывания информация, хранимая в некотором месте памяти, переводится на выходные шины ОЗУ. Выбор конкретного места памяти для записи и считывания осуществляется подачей адресного слова на дешифратор адреса, обычно расположенный внутри ОЗУ. Дешифратор выбирает ячейку памяти, определенную кодом адресного сЛова. Для запоминания аналогового переходного процесса ОЗУ переводится в режим записи. По началу переходного процесса производится его дискретизация и оцифровка. Значения цифровых выборок вводятся в ячейку ОЗУ при одновременном увеличении содержимого счетчика адреса памяти. Этот процесс продолжается до тех пор, пока не будут заняты все ячейки памяти непрерывной записью цифровых выборок переходного процесса входного аналогового сигнала. Для восстановления аналогового переходного процесса из его запомненных выборок ОЗУ переводится в режим считывания. Содержимое счетчика адреса увеличивается на единицу по каждому тактовому импульсу, вызывая появление последовательности цифровых выборок на выходных шинах ОЗУ. ЦАП преобразует выбор-ки в аналоговую форму. Когда счетчик адреса переполняется, снова повторяется цикл и восстановленный аналоговый переходный процесс периодически вырабатывается на выходе ЦАП. Переходный процесс может тактироваться со скоростью, которая удобна для использования конкретного типа устройства воспроизведения аналогового сигнала. Медленная скорость тактирования используется в Устройство управления ОЗУ! :з|> Микроэвм -I/, бых Рис. 12.9. Структурная схема цифровой системы временного сжатия и растяжения аналоговых, сигналов перьевом записывающем устройстве, более быстрые тактовые импульсы требуются для повторяющегося отображения на осциллографе. , Быстродействующее ОЗУ в сочетании с быстродействующим АЦП может использоваться для записывающего устройства изменяющихся jc высокой скоростью переходных процессов аналоговых сигналов. Системы такого рода применяются для наблюдения переходных процессов, которые происходят, например, при исследовании ударов или взрывов. Быстродействующие преобразователи в сочетании с быстродействующими устройствами находят также применение в цифровой обработке телевизионных сигналов (см. гл. 10). При создании на базе ЭВМ аппаратуры для контроля качества быстродействующих аналоговых и аналого-цифровых приборов большое распространение получило временное сжатие и растяжение сигналов. Для этого между выходом АЦП и входом ЦАП включают два буферных запоминающих устройства ОЗУ1 и ОЗУ2 (рис. 12.9). Для микроэвм эти ОЗУ являются внешними устройствами, тактовая частота работы которых задается внешним генератором. Последний синхронизирует работу ОЗУ, ЦАП и АЦП. Такая структура системы позволяет с высокой тактовой частотой выполнить преобразование аналогового сигнала в течение конечного времени его изменения и записать результат преобразования М выборок Свх в ОЗУ1 в виде цифровых уУ-разрядных слов. Затем с помощью микроЭВМ можно выполнить обработку информации об изменении аналогового сигнала со значительно более низкой частотой исполнения команд в микроэвм. Таким образом осуществлено как бы растяжение сигнала во времени. По результатам такой цифровой обработки аналогового сигнала или в соответствии с программой работы микроэвм сравнительно медленно может быть записана информация в ОЗУ2. Затем если с тактовой частотой, которая больше частоты входных выборок М, на вход ЦАП из ОЗУ2 выдавать цифровые слова, преобразуемые в аналоговый сигнал, то можно осуществлять сжатие сигнала. Динамические параметры прини- маемого и формируемого аналоговых сигналов определяются динамическими характеристиками преобразователей и ОЗУ и не зависят от бы.стродействия микроЭВМ. Используя такую систему обработки сигналов можно, например, провести полный анализ точностных характеристик любых аналого-цифровых и аналоговых приборов в реадьных условиях работы. Например, включив в схему иссле-дуемь1Й АЦП, как показано на рис. 12.9, и замкнув ее выход со ВХОДОМ, можно проверить работу АЦП в режиме преобразования аналоговых сигналов с любыми параметрами [76]. Обеспечивая возможность цифровой обработки аналоговых сигналов в диапазоне частот вплоть до единиц мегагерц, описанные системы на базе БИС общего применення не позволяют существенно уменьшить габариты и потребляемую мощность аппаратуры. Решение проблемы снижения габаритов и энергопотребления аппаратуры цифровой обработки по сравнению с аппаратурой аналоговой обработки стало возможным только после создания специализированных БИС. Первыми такими БИС стали быстродействующие цифровые умножители и сумматоры. Скорость выполнения операции умножения является критерием эффективности любого процесса обработки сигналов. Эта операция как раз и относится к числу цаиболее медленно реализуемых в микроЭВМ общего применения. Специализированные БИС умножителей определяют принципы построения процессорной части системы обработки. Исходя из этого первые процессоры сигналов, как правило, разделяли на конвейерные, матричные и последовательно-параллельные [77]. Наибольшим быстродействием обладают процессоры сигналов с матричными умножителями, которые, однако, являются наиболее сложными И анергопотребляющими. Операция суммирования необходима для реализации большинства алгоритмов спектрального анализа и, в частности, при выполнении быстрого преобразования Фурье. На основе микропроцессорных комплектов общего применения и специализированных БИС цифровых умножителей и сумматоров можно построить процессоры сигналов, обладающие определенной универсальностью. Именно так .строились первые процессоры цифровой обработки аналоговых сигналов, которые обладали сравнительно высокой производительностью (до 10 операций умножения за секунду), возможностью реконфигурации и программирования. Обычно эти процессоры были ориентированы на реализацию основных видов операторов (свертка, рекурсия, дискретное преобразова-IHfc Фурье, нелинейное и логическое преобразования), необходимых пр обработке аналоговых сигналов. В конце 70-х годов в показателях качества цифровых приборов обработки аналоговых сигналов произошел новый качественный скачок благодаря выпуску зарубежными фирмами нескольких типов однокристальных процессоров сигналов [78]. В отличие от ранее выпущенных приборов цифровой обработки сигналов однокри- стальные процессоры сигналов были ориентированы в основном на выполнение операций свертки, рекурсии и дискретного преобразования Фурье. Сокращение набора реализуемых операторов было вызвано необходимостью упростить арх^ектуру процессора сигналов в соответствии с конструктивно-технологическими требованиями современной промышленности полупроводниковых микросхем. При этом по сравнению с универсальными однокристальными микроЭВМ аналогичной стоимости и потребляемой мощности в процессорах сигналов была получена почти в 100 раз большая производительность (время выполнения операции умножения). , Переьщ отечественным однокристальным ироцессором аналоговых сигирлов стала БИС КМ1813РЕ1. Этот аналоговый микропроцессор сортоит из трех фучвдионльных частей; АЦП. микроЭВМ и ЦАП (рис 12.10). Его архитектура рассчитана иа реализацию операций суммироеанич парных произведений за минимальное время. Одновременно с высокой рроизводительностью выполнения указанных операций эта рПС обладает гибкостью применения благодаря возможности ее перепрограммирования [79]. В БИС KM1813BEJ ЦАЦ и АЦП образуют устройства ввода-вырода аналоговых сигналов (УВВ), цифровая обработка которых выполняется в верхней части схемы цифрового процессрра обработки сигналов (UnOCj. В реррограммируемое ПЗУ записывается программа работы UN/PROG  Рис. 12.J0- Структурная схема аналогового микропроцессора КМ1813ВЕ1 - процессора Устройства ввода-вывода аналоговых сигналов обеспечивают многоканальный режим работы благодаря использованию четырехканального входного мультиплексора и восьмиканального мультиплексора на выходе ЦАП [80]. Аналого-цифровое преобразование реализуется методом последовательного приближения. Для этого входное УВХ по командам из блока управления и ЦПОС запоминает мгновенное значение выбранного аналогового сигнала. Запоминающий конденсатор для УВХ является внещним. Время выборки УВХ обратно пропорционально емкости Сз этого конденсатора, которую рекомендуется выбирать в диапазоне 100 ... 1000 пФ. Максимальную емкость конденсатора необходимо устанавливать при минимальной тактовой частоте для уменьщения влияния ощибки хранения на -ТОЧНОСТЬ. АЦП обеспечивает преобразование с точностью, соответствующей девяти разрядам. При максимальной емкости запоминающего. конденсатора требуемая точность выборки входного аналогового сигнала достигается при последовательном выполнении восьми команд ввода /N{K). Затем в результате исполнения серии инструкций CVT(n) аналоговый сигнал последовательно преобразуется в цифровое 9-разрядное слово, у которого 1-й разряд соответствует знаковому, а 9-й разряд является старщим значащим. Для полного цикла преобразования необходимо выполнить 34 команды, что при максимальной тактовой частоте, равной 6,67 МГц, соответствует времени . преобразования, равному 20 мкс. Если допустимо уменьщение точности преобра зования, то можно, прервав процесс преобразования исполнением меньшего числа команд, уменьшить и время преобразования. Например, преобразование с точностью, соответствующей шести разрядам, можно выполнить примерно за 10 мкс. Обмен данными между аналоговой и цифровой частями БИС осуществляется через цифровой адресуемый регистр. (ЦАР) данных, который имеет адрес ячейки номер 40 в ОЗУ (при программировании этот регистр обозначается DAR). В ЦАР запоминается результат преобразования, который может быть затем переадресован в любую ячейку ОЗУ и, следовательно, использован как операнд арифметико-логического устройства (АЛУ) или через ЦАП и выходной мультиплексор выдан на выход БИС. Номер канала задается инструкцией OU/T(K). Для заряда запоминающего конденсатора выходного УВХ любого канала до точности соответствующей девяти разрядам при максимальной тактовой частоте требуется исполнение восьми- инструкций OUT(K). В каждом выходном канале установлены индивидуальные УВХ и усилитель. В выходных УВХ использованы внутренние запоминающие конденсаторы. Для работы ЦАП и АЦП необходим внешний прецизионный источник опорного напряжения с напряжением 1 ... 2 В, подключаемый к выводу 8. Стабильность опорного напряжения должна быть не меньше 0,2%. В схеме предусмотрены две общие точки питания: вывод 17 для ЦПОС и вывод 4 для УВВ. Возможные режимы работы по каналам ввода и вывода приведены в табл. 12.1. Управление режимами работы УВВ осуществляется по выводам 24. и 25 как для аналоговых, тя и цифровых сигналов. При различных сочетаниях напряжений на этих выводах могут быть использованы входные каналы О-3 и выходные каналы О-7 для работы с аналоговыми и цифровыми сигналами. Репрограммируемое ПЗУ с ультрафиолетовым стиранием обеспечивает запись 192 слов по 24 разряда. В каждое слово упаковыв.аются две инструкции для исполнения аналоговой (УВВ) и цифровой (ЦПОС) частями БИС. Это 24-раз- Таблица 12.1 Режимы ввода-вывода БИС КМ1813ВЕ1

рядное слово разбито на пять полей, из которых одно 5-разрядное поле управляет аналоговой частью БИС, а остальные четыре управляют цифровой частью (рис. 12.11). В цифровой части команд L-три разряда поля команды АЛ У; В - шесть разрядов поля операнда В; А - шесть разрядов поля операнда А; S - четыре разряда поля сдвига. В аналоговой части команд ADT - два разряда селектора функций; ADK - три разряда модификатора. При работе БИС доступ ко всем ячейкам памяти команд в РПЗУ последовательный. Код счетчика команд в БИС возвращается в ячейку О после завершения выполнения команды 191 или когда в аналоговом поле команд встречается инструкция Конец программы или Возврат по условию . Каждая команда выполняется за четыре такта работы задающего генератора. Команды из РПЗУ считываются четверками (всего 48 четверок) и записываются в 96-разрядный регистр. Считывание из РПЗУ каждой четверки команд сопровождается сигналом на выводе 19. Память данных построена на ОЗУ статического типа с произвольной выборкой одновременно двух 25-разрядных слов и регистрах для хранения операндов А и В. Емкость ОЗУ составляет 40 слов. Свободная область значений 6-разрядного адреса А используется для задания констант в программе. Обращение к константам осуществляется только через, порт А по 16 старшим адресам пространства адресов. При этом значения четырех младших разрядов адреса А присваиваются четырем старшим разрядам поля данных порта А. Всего может задаваться 16 констант в диапазоне от -10 до --0,875 с шагом 0,125. Мнемонические обозначения констант и их значения приведены в табл. 12.2. При программировании константы записываются только в поле операнда А. Признаком константы является единичное значение обоих старших разрядов адреса А, т. е. если значение адреса А больше или равно 48, то четыре младших разряда адреса А воспринимаются как константа, и через порт А поступают иа вход АЛУ. Рис. 12.11. Формат команды, используемой в БИС КМ1813ВЕ1

Таблица 12.2 Константы РПЗУ

В ОЗУ по адресу 40 (1010000-) размещается регистр ЦАР, который занимает девять старших разрядов 25-разрядного слова. Выходы регистра подключены к ЦАП. Любой разряд регистра может анализироваться и устанавливаться в соот- ветствии со -значением разряда переполнения. Регистр ЦАР также используется в качестве регистра последовательного приближения при выполнении аналого-цифрового преобразования под управлением аналоговых команд. При считывании содержимого ЦАР в АЛУ все разряды, кроме девяти старших, принимают значения, равные единице. Масштабирующее устройство представляет собой арифметический двоичный сдвиговый регистр, осуществляющий масштабирование содержимого порта А при передаче его на вход АЛУ. Диапазон сдвига - до двух разрядов влево и до 13 разрядов вправо. Масштабировать операнд В и результат вычисления нельзя. При сдвиге влево освобождающиеся правые разряды заполняются нулями, а при сдвиге вправо - значением знакового разряда. Арифметико-логическое устройство обрабатывает 25-разрядный масштабированный операнд А и операнд В, извлекаемые из ОЗУ. Результат записывается в память по адресу В в конце цикла выполнения команды. Арифметико-логическое устройство использует 28-разрядную сетку, где разряды 26 и 27 фиксируют старшие разряды числа при сдвиге его влево, а разряд 28 обеспечивает выполнение операций переноса. В разрядной сетке четыре старших разряда знаковые. Факт переполнения фиксируется, если знаковые разряды становятся разными. Это означает, что результат сдвига или арифметической операции выходит за границы -1,0...--1,0. В АЛУ программно может устанавливаться режим ограничения переполнения, при котором результат переполнения заменяется ближайшим к истинному результату, т. е. -1,0, если результат отрицательный, и +1,0, если результат положительный. Такой режим полезен с точки зрения устойчивости фильтров, уменьшения их шумов. Он также может использоваться для реализации нелинейных функций, например ограничения. Таким образом, может имитироваться режим насыщения усилителя [80]. Сигнал на выводе 22 указывает, что в выполняемой команде имело место переполнение. Если переполнение не запрещено, то каждое двоичное число может расширяться до 28 разрядов путем перемещения знакового разряда влево. Выполняется соответствующая операция АЛУ, и младшие 25 разрядов результата записываются в ОЗУ по адресу операнда В. Систему команд БИС КМ1813ВЕ1 можно разбить на две группы: цифровые команды АЛУ и аналоговые для УВВ. В свою очередь, цифровые команды разде 1 ... 31 32 33 34 35 36 37 38 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||